Amazon.com: Mouse Pad, Gaming Mouse pad with Additional 4-Port USB Hub, 31.5 x 11.8 x 0.2 inches Thickened RGB Mouse Pad,14 Colors to Switch at Will… : Office Products

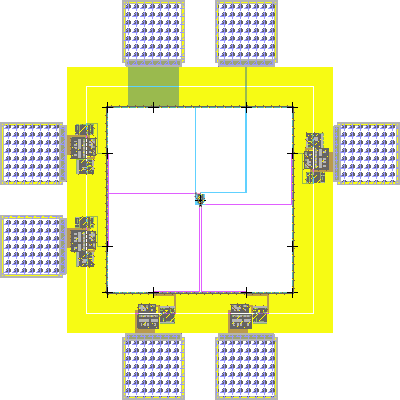

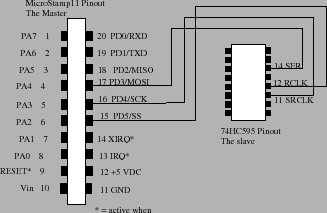

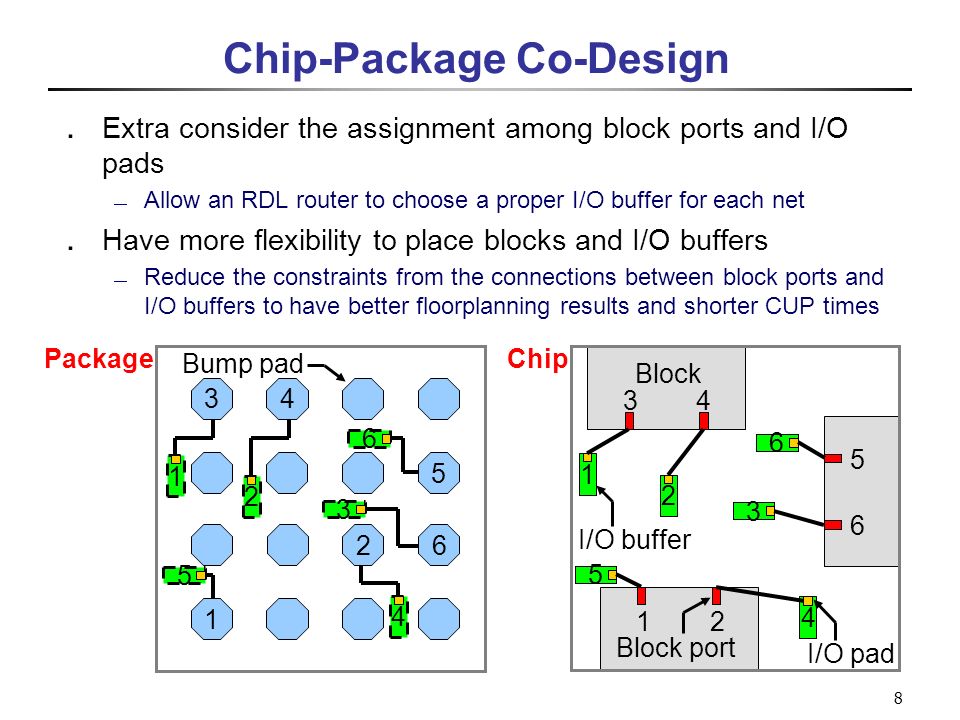

Area-I/O Flip-Chip Routing for Chip-Package Co-Design Progress Report 方家偉、張耀文、何冠賢 The Electronic Design Automation Laboratory Graduate Institute of Electronics. - ppt download